内容很多,而且真的是概述。。。

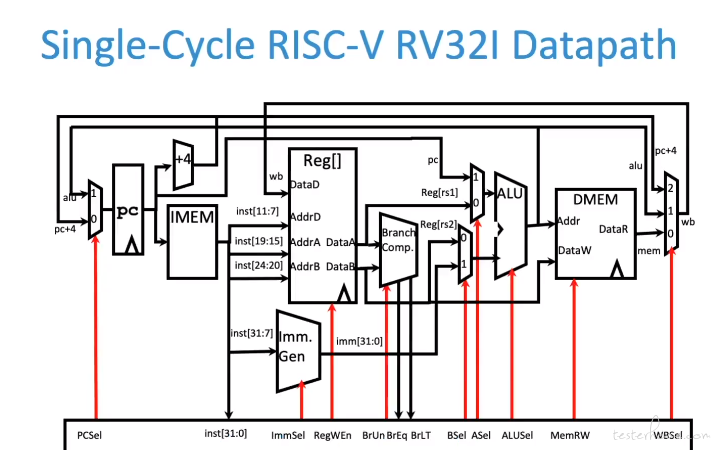

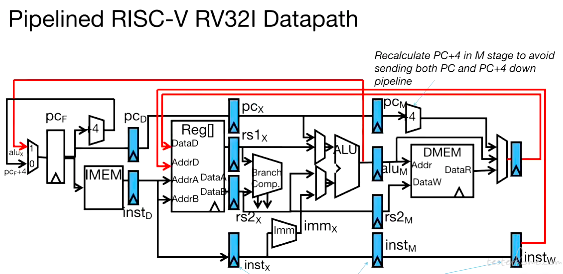

数据通路

RSIC-V 的设计思想是:

不同的指令用同一个数据通路,每个指令用不同的控制信号来控制状态和操作:

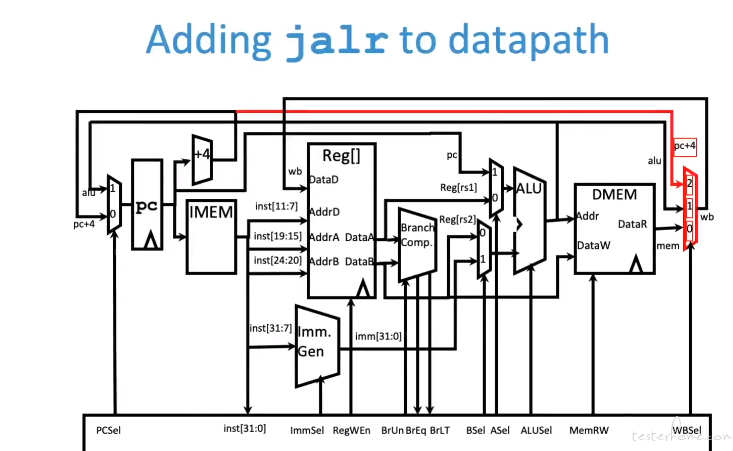

BRANCH 跳转和 jalr 对数据通路设计的影响:

性能分析

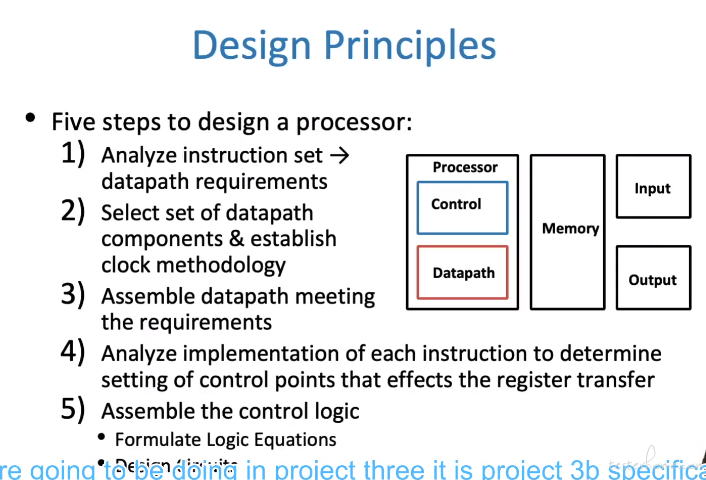

设计准测

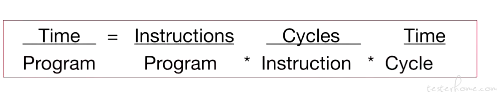

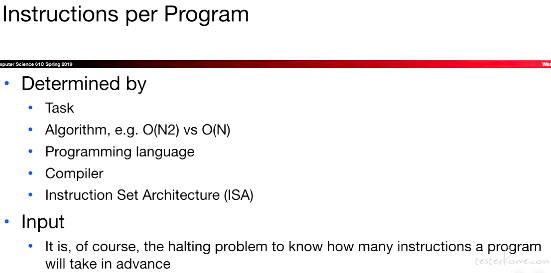

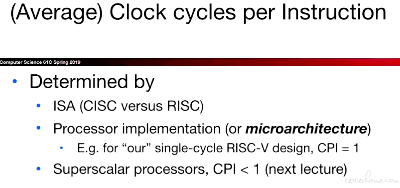

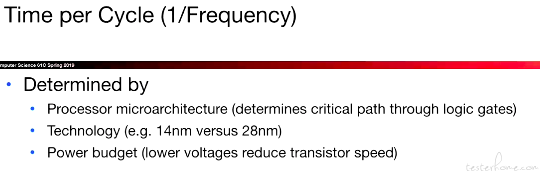

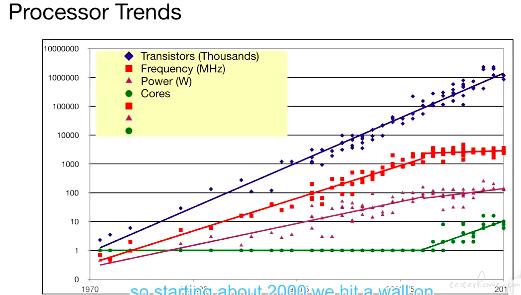

时间性能

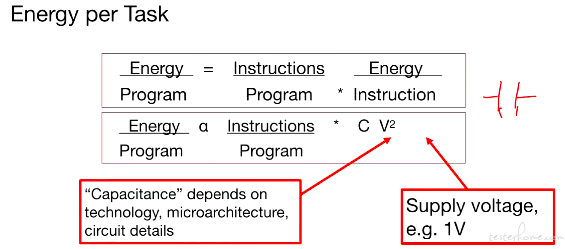

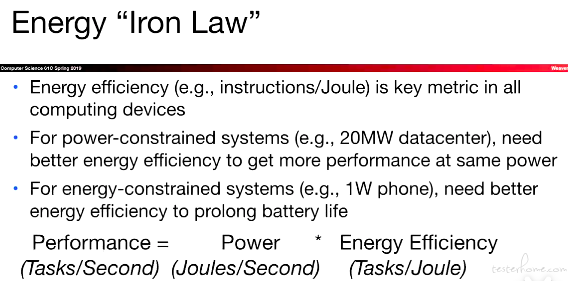

功耗性能

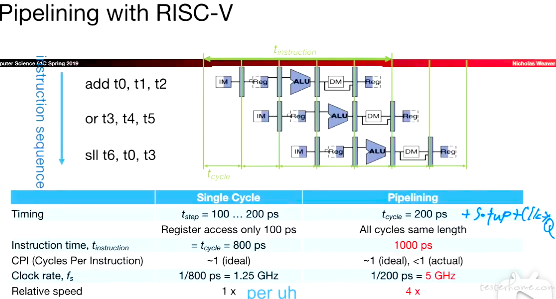

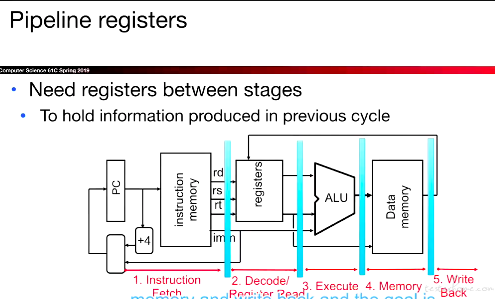

流水线设计

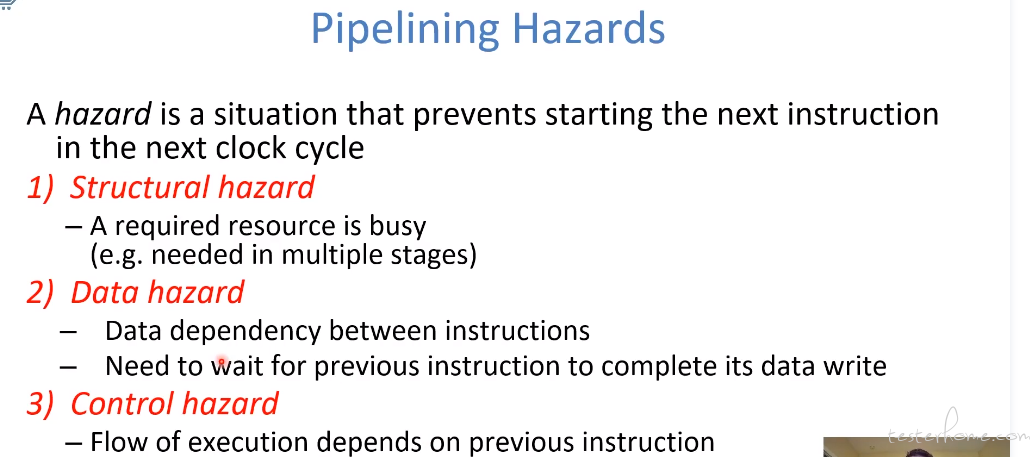

流水线风险:

结构化风险解决办法:

- 按顺序等待指令

- 加硬件

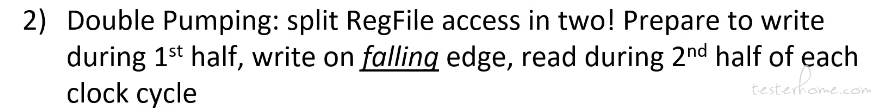

对于寄存器基本用的是这个方法:

- 数据和指令 CACHE 分离,比如 CPU 的 L1 CACHE,GPU 的 L1 CACHE。

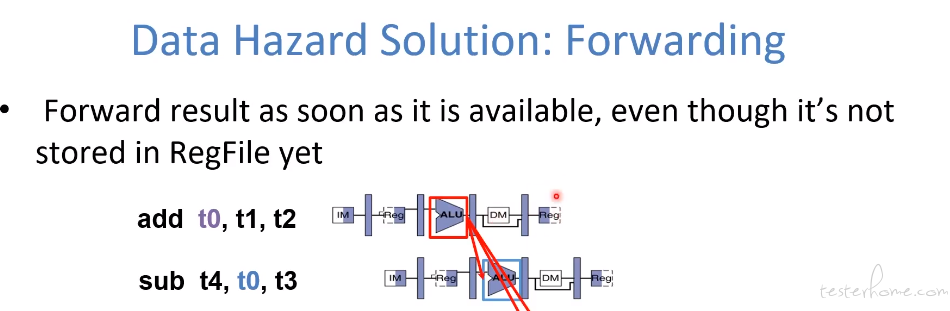

数据风险解决办法

1.

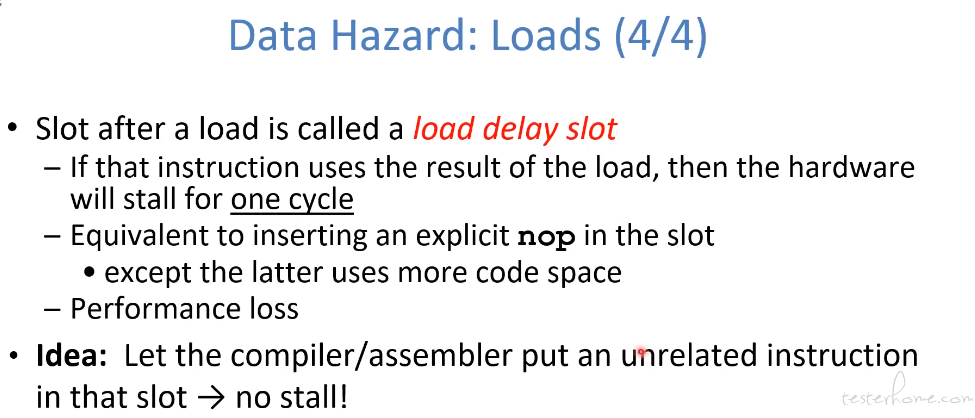

对于 RAW,后续指令依赖前面指令的读取内存结果,Forward 是无效的。

通常硬件会加入 nop 指令。

可以通过更加优化的编译器,对指令进行重排。。。

控制风险

控制风险主要是跳转指令。

分支预测在 GT(佐治亚理工) 的 CS6220 里面介绍的稍微更细节一些。

暂无回复。